Welcome! I am a PhD candidate in the ECSE Department at Rensselaer Polytechnic Institute, advised by Tong Zhang. I earned my BE in Southern University of Science and Technology.

My research focuses on optimizing memory architectures, primarily DRAM and SSDs, to enhance hardware performance and software efficiency. I explore solutions in data processing and AI, aiming to contribute to more efficient and sustainable computing systems.

Feel free to reach out. I am always happy to chat! 📧 Email: xier2 [at] rpi (dot) edu

🏫 Education

PhD Candidate in Computer & Systems Engineering — Rensselaer Polytechnic Institute

📍 Troy, NY, USA | 🗓️ 2022 – Present

BE in Microelectronics Science and Engineering — Southern University of Science and Technology

📍 Shenzhen, China | 🗓️ 2018 – 2022

💼Experience

Platform & ASIC Research Intern — Nokia Bell Labs

📍 Murray Hill, NJ, USA | 🗓️ 2025

EDA Engineer Intern — BTD Technology

📍 Shenzhen, China | 🗓️ 2021 – 2022

Research Intern — University of Hong Kong

📍 Hong Kong SAR, China | 🗓️ 2020

Visiting Student — University of Oxford

📍 Oxford, UK | 🗓️ 2019

📕Publications

-

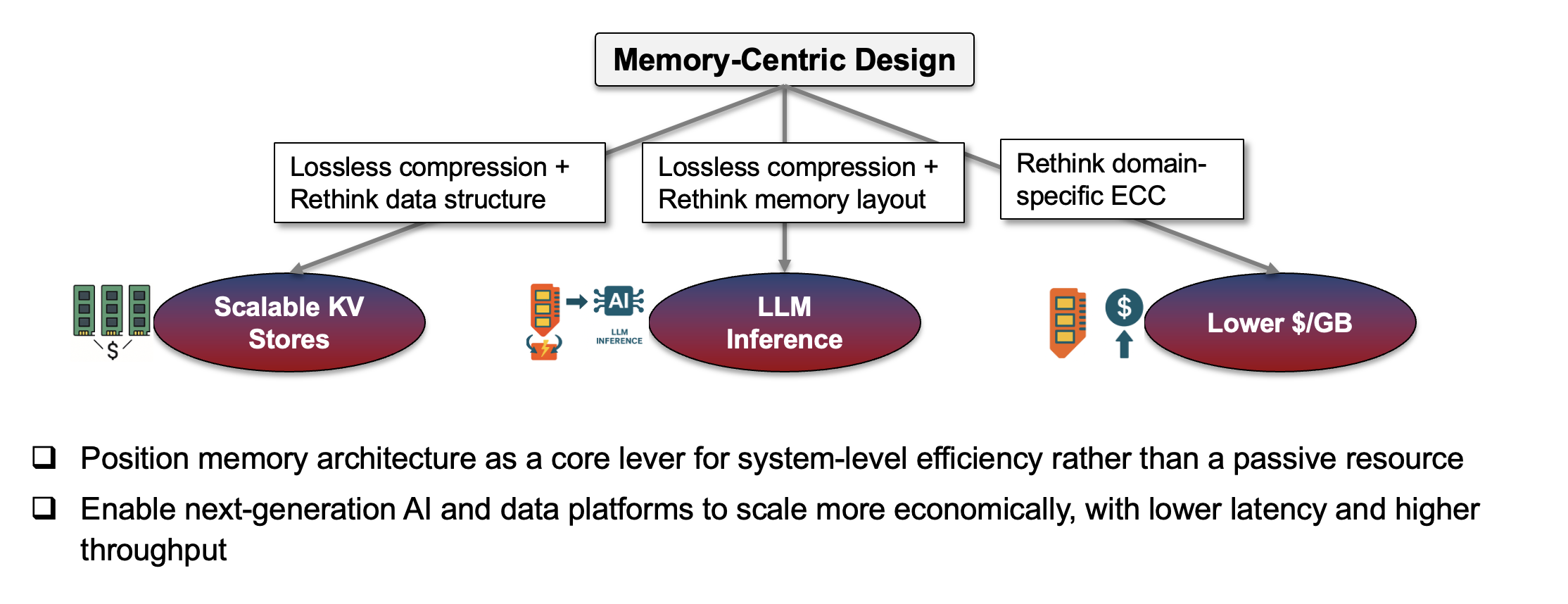

Rui Xie, Asad Ul Haq, Yunhua Fang, Linsen Ma, Sanchari Sen, Swagath Venkataramani, Liu Liu, Tong Zhang, “Breaking the HBM Bit Cost Barrier: Domain-Specific ECC for AI Inference Infrastructure”, arXiv preprint arXiv:2507.02654 (paper)

-

Rui Xie, Asad Ul Haq, Linsen Ma, Yunhua Fang, Zirak Burzin Engineer, Liu Liu, Tong Zhang, “Reimagining Memory Access for LLM Inference: Compression-Aware Memory Controller Design”, arXiv preprint (paper)

-

Rui Xie, Linsen Ma, Alex Zhong, Feng Chen, Tong Zhang, “ZipCache: A Hybrid-DRAM/SSD Cache with Built-in Transparent Compression”, 10th International Symposium on Memory Systems (paper) (slides)

-

Rui Xie, Asad Ul Haq, Linsen Ma, Krystal Sun, Sanchari Sen, Swagath Venkataramani, Liu Liu, Tong Zhang, “SmartQuant: CXL-based AI Model Store in Support of Runtime Configurable Weight Quantization”, arXiv preprint (paper)

-

Linsen Ma, Rui Xie, Tong Zhang, “ZipKV: In-Memory Key-Value Store with Built-In Data Compression”, 2023 International Symposium on Memory Management (paper)

-

Ziyi Guan, Wenyong Zhou, Yuan Ren, Rui Xie, Hao Yu, Ngai Wong, “A Hardware-Aware Neural Architecture Search Pareto Front Exploration for In-Memory Computing”, in Proc. 2022 IEEE 16th Int. Conf. Solid-State and Integrated Circuit Technology (ICSICT), Oct 2022 (paper)

-

Yuan Ren, Wenyong Zhou, Ziyi Guan, Rui Xie, Quan Chen, Hao Yu, Ngai Wong, “XMAS: An Efficient Customizable Flow for Crossbarred-Memristor Architecture Search”, 59th Design Automation Conference Engineering Track (poster)

-

Rui Xie, Mingyang Song, Junzhuo Zhou, Jie Mei, Quan Chen, “A Fast Method for Steady-State Memristor Crossbar Array Circuit Simulation”, 2021 IEEE International Conference on Integrated Circuits Technologies and Applications (paper)

-

Quan Chen, Dayi Fan, Rui Xie, Mingyang Song, “Construction and optimization of neural networks for memristor arrays based on circuit simulation”. CN 202110673101.5 (patent)

🏆 Honors and Awards

-

Outstanding Innovation Award 2nd Place Winner, Nokia Bell Labs - 2025

-

DAC Young Fellow Award, 61th Design Automation Conference - 2024

-

Excellent Graduate Award, Southern University of Science and Technology — 2022

-

First Class Student Scholarship (Top 5%), Southern University of Science and Technology — 2021

-

First Prize of College Student Innovation and Entrepreneurship Training Program, Southern University of Science and Technology - 2021

📒 Peer Reviewer Experience

- IEEE International Symposium on Circuits and Systems - 2022, 2023, 2024